# STUDY OF DYNAMIC VOLTAGE RESTORER FOR DISTRIBUTION WITH DIFFERENT ENERGY STORAGE OPTIONS

U. N. Sanjaya

(109253A)

Dissertation submitted in partial fulfillment of the requirements for the degree Master of Science

Department of Electrical Engineering

University of Moratuwa Sri Lanka

May 2015

# Declaration, copyright statement and the statement of the supervisor

I declare that this is my own work and this thesis/dissertation does not incorporate without acknowledgement any material previously submitted for a Degree or Diploma in any other University or institute of higher learning and to the best of my knowledge and belief it does not contain any material previously published or written by another person except where the acknowledgement is made in the text.

Also, I hereby grant to University of Moratuwa the non-exclusive right to reproduce and distribute my thesis/dissertation, in whole or in part in print, electronic or other medium. I retain the right to use this content in whole or part in future works (such as articles or books).

| And with             | University of Mora<br>Electronic Theses &<br>www.lib.mrt.ac.lk<br>e has carried out research |       | on under my |

|----------------------|----------------------------------------------------------------------------------------------|-------|-------------|

| supervision.         |                                                                                              |       |             |

|                      |                                                                                              |       |             |

|                      |                                                                                              |       |             |

| Internal supervisor: |                                                                                              | Date: |             |

| Prof. J.P. Karunada  | sa                                                                                           |       |             |

|                      |                                                                                              |       |             |

|                      |                                                                                              |       |             |

| External supervisor  | :                                                                                            | Date: |             |

Dr. H. M. Wijekoon

#### **Abstract**

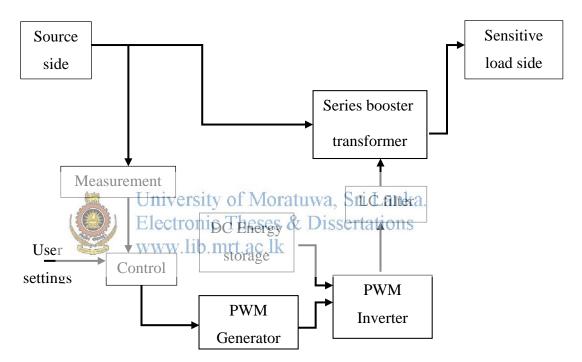

Present Power quality problems in distribution systems have been increased due to the increased utilization of sensitive and critical equipment in the system. Power quality issues may contain transient over voltages, voltage sags, voltage swells, under voltage, overvoltage, harmonics distortion, flicker and voltage imbalance, etc. One of the most severe power quality problems is voltage sag. Among the various solutions to overcome power quality problems, Dynamic Voltage Restorer (DVR) is one of the most effective solutions. The DVRs can be used to mitigate voltage sags/swells by injecting an appropriate voltage in series with the grid voltage, in order to avoid loss of power as it can maintain the load voltage at its nominal magnitude and phase by compensating the particular voltage sag/swell. The DVR consists of a series connected injection transformer, a Voltage Source Inverter (VSI), inverter output filter and a DC energy storage.

DC storage mainly decides the capability of DVR. This dissertation is based on study of the technical and economic aspects of various DC energy storage options on the performance of DVR in the Voltage restoration.

The most common DC energy storage such as Batteries, Conventional Capacitors and the recently developed storage technology "Super capacitors" have been discussed here. MATLAB Simulink platform was used for modeling and simulating the DVR and the energy storage options. Other than the standard DC energy storage models, a new model was built up for Super capacitor and validated through experiential results. Further economics of the above energy storage options in achieving the required energy storage levels have been investigated.

Based on the responses of DVR in different types of sags and swells for the above energy storage options it can be concluded that for deeper and short duration sag mitigations, super capacitor performs better. But in mitigating longer duration sags, battery performs better. Conventional capacitor storages manufactured in the same scale of super capacitors can perform better than batteries, but in the economic point of view it is not appropriate.

# Acknowledgement

I would like to extend my sincere gratitude to my internal supervisor, Prof. J.P. Karunadasa for his great insight guidance in this study. Also, as the head of the department, he gave me all the helping hands for all the laboratory experiments carried out in the Department of Electrical Engineering. In addition, I must appreciate the coordinator of the Post Graduate Division of the Department of Electrical Engineering, Dr. Asanka Rodrigo for all the assistance given to me.

Further, I wish to thank my external supervisor Dr. H.M. Wijekoon who suggested this research concept and made me realized about the aims of this study.

In addition, I shall be grateful to the staff of the Department of Electrical Engineering who assisted me in the laboratory experiments and other documentation work.

Finally I should thank all my colleagues for who haven't been mentioned personally

Electronic Theses & Dissertations

www.lib.mrt.ac.lk

for making this study a success.

University of Moratuwa, Sri Lanka.

iii

# TABLE OF CONTENTS

| Declaration,  | , copyright statement and the statement of the supervisor        | i   |

|---------------|------------------------------------------------------------------|-----|

| Abstract      |                                                                  | ii  |

| Acknowledg    | gement                                                           | iii |

| TABLE OF      | CONTENTS                                                         | iv  |

| LIST OF FI    | GURES                                                            | vii |

| LIST OF TA    | ABLES                                                            | X   |

| LIST OF A     | BBREVIATIONS                                                     | xi  |

| Chapter 1     |                                                                  | 1   |

| 1.0 INTE      | RODUCTION                                                        | 1   |

| 1.1 Po        | wer Quality of Distribution Network                              | 1   |

| 1.2 Mi        | itigating the Power Quality Issues                               | 1   |

| 1.3 <b>Ob</b> | jective of the study of Moratuwa, Sri Lanka.                     | 3   |

| 1.4 Sc        | Electronic Theses & Dissertations of the Study www.lib.mrt.ac.lk | 3   |

|               | terature review                                                  |     |

| Chapter 2     |                                                                  | 5   |

| 2.0 STU       | DY OF THE DYNAMIC VOLTAGE RESTORER AND DC                        |     |

| ENERGY S      | TORAGE                                                           | 5   |

| 2.1 Lo        | cating the DVR for line conditioning                             | 5   |

| 2.2 Eq        | uation Related to DVR                                            | 6   |

| 2.3 Co        | onventional System of DVR                                        | 6   |

| 2.4 Ba        | sic elements of DVR                                              | 7   |

| 2.4.1         | Series booster/injection transformer                             | 8   |

| 2.4.2         | Passive filter                                                   | 8   |

| 2.4.3         | Voltage Source Converter                                         | 9   |

| 2.4.4         | Control and Voltage injection Scheme                             | 10  |

| 2.4.5         | DC Energy Storage with charging mechanism                        | 11  |

| Chapter | 3                                                                     | 18 |

|---------|-----------------------------------------------------------------------|----|

| 3.0 F   | RESEARCH METHODOLOGY                                                  | 18 |

| 3.1     | Modelling the MV and LV distribution feeders                          | 18 |

| 3.1.    | 1 Modeling the 33kV Feeder bay and the MV line                        | 18 |

| 3.1.    | 2 Modeling the Distribution Transformer                               | 18 |

| 3.1.    | Modelling the sensitive load                                          | 19 |

| 3.1.    | 4 Creating the Voltage Sag and Swell                                  | 19 |

| 3.2     | Modelling the DVR                                                     | 19 |

| 3.2.    | Modeling the Series Injection Transformer                             | 20 |

| 3.2.    | 2 Modeling the IGBT converter                                         | 20 |

| 3.2.    | Modelling the LC filter                                               | 20 |

| 3.2.    | 4 Modelling the control system                                        | 20 |

| 3.3     | Testing the model for voltage compensation                            | 21 |

| 3.3     | Testing for Single phase voltage sage reations                        | 23 |

| 3.3.2   | Pesting for 3 phase sags c. 1k                                        | 24 |

| 3.3.    | Testing for voltage swells                                            | 25 |

| 3.4     | Modeling the DC Energy Storage for DVR                                | 29 |

| 3.4.    | Modeling the Battery Energy Storage                                   | 29 |

| 3.4.    | 2 Modelling the Super capacitor Energy Storage                        | 31 |

| 3.4.    | Modeling the conventional capacitor Storage                           | 38 |

| Chapter | 4                                                                     | 39 |

| 4.0 F   | RESULTS AND DISCUSSION                                                | 39 |

| 4.1     | Integration of the battery energy storage with the DVR                | 39 |

| 4.2     | Integration of the super capacitor energy storage with the DVR        | 44 |

| 4.2.    | 1 Harmonics of injected voltage                                       | 50 |

| 4.3     | Integration of the conventional capacitor energy storage with the DVR | 55 |

| Chapter | 5                                                                     | 58 |

| 5.0    | ECONOMIC ANALYSIS              | 58 |

|--------|--------------------------------|----|

| 5.1    | Ni-MH battery storage          | 58 |

| 5.2    | Super capacitor storage        | 58 |

| 5.3    | Conventional capacitor storage | 59 |

| Chapte | er 6                           | 62 |

| 6.0    | CONCLUSION                     | 62 |

| Refer  | ence List                      | 64 |

# LIST OF FIGURES

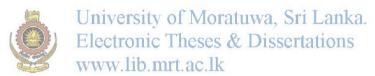

| Figure 2.1: Location of DVR in LV side                                          | 5   |

|---------------------------------------------------------------------------------|-----|

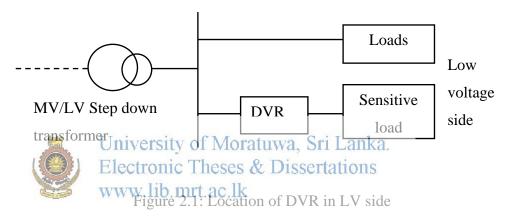

| Figure 2.2: Location of DVR in MV side                                          | 5   |

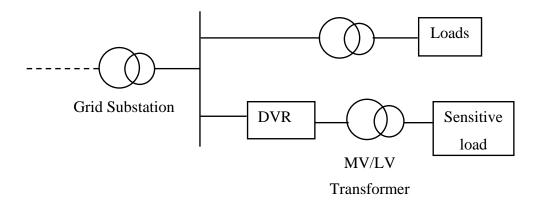

| Figure 2.3: Circuit Model of DVR installed in a line                            | 6   |

| Figure 2.4: Simplified block demonstration of DVR                               | 7   |

| Figure 2.5: Passive LC filter                                                   | 9   |

| Figure 2.6: Six pulse Voltage Source Converter                                  | 9   |

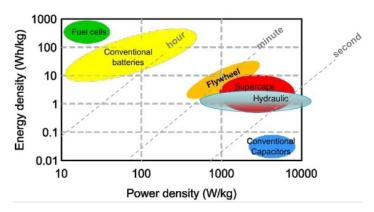

| Figure 2.7: Technical capabilities of the energy storage options                | .11 |

| Figure 2.8: Power and Energy Density of Storage options                         | .12 |

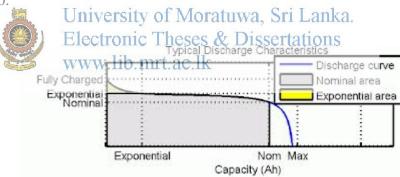

| Figure 2.9: Equivalent Electrical Model of a Battery                            | .13 |

| Figure 2.10: Typical Discharge Characteristics of Battery Storage               | .13 |

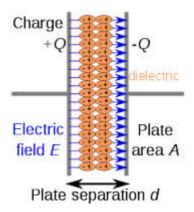

| Figure 2.11: Structure of a Conventional Capacitor                              | .14 |

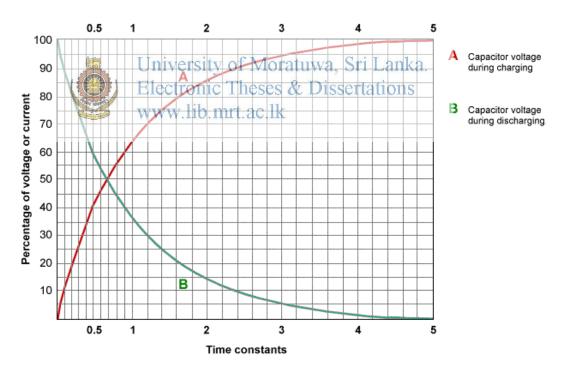

| Figure 2.12: Charging and discharging characteristics of conventional capacitor | .14 |

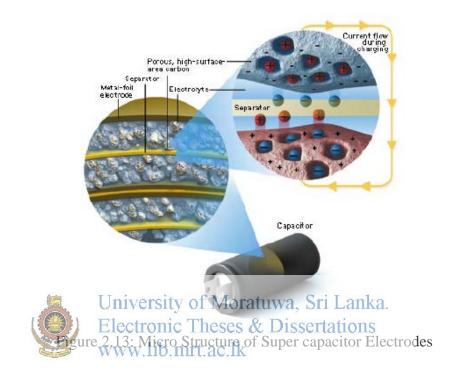

| Figure 2.13: Micro Structure of Super capacitor Electrodes                      | .15 |

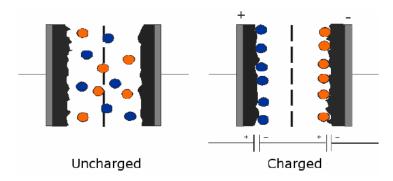

| Figure 2.14: Structure of Uncharged and Charged Super capacitor                 | .16 |

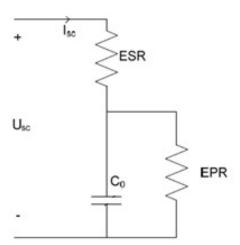

| Figure 2.15: Equivalent Electrical Model of a Super capacitor                   | .16 |

| Figure 2.16: Charging and discharging characteristics of Super capacitor        | .17 |

| Figure 3.1: Control system of Evrity of Moratuwa, Sri Lanka.                    | .21 |

| Figure 3.2: Electronic Theses & Dissertations                                   | .22 |

| Figure 3.3: Voltage measured at Source side for single phase sag                | .23 |

| Figure 3.4: Voltage Injected by DVR to Compensate the Sag                       | .23 |

| Figure 3.5: Voltage measured at sensitive load side for single phase sag        | .24 |

| Figure 3.6: Voltage measured at Source side for three phase sag                 | .24 |

| Figure 3.7: Voltage Injected by DVR to Compensate the Sag                       | .25 |

| Figure 3.8: Voltage measured at sensitive load side for three phase sag         | .25 |

| Figure 3.9: Testing the DVR model for voltage swells                            | .26 |

| Figure 3.10: Voltage measured at Source side for single phase swell             | .27 |

| Figure 3.11: Voltage Injected by DVR to Compensate the Swell                    | .27 |

| Figure 3.12: Voltage measured at sensitive load side for single phase swell     | .28 |

| Figure 3.13: Voltage measured at Source side for three phase swell              | .28 |

| Figure 3.14: Voltage Injected by DVR to Compensate the Swell                    | .28 |

| Figure 3.15: Voltage measured at sensitive load side for single phase swell     | .29 |

| Figure 3.16: Testing the charging characteristics of the battery                | .29 |

| Figure 3.17: Constant current charging characteristics of battery               | .30 |

| Figure 3.18: Battery charging characteristics manufacturer's data               | .30 |

| Figure 3.19: Super capacitor MATLAB model                                       | .31 |

| Figure 3.20: Testing the super capacitor charging characteristics               | .32 |

| Figure 3.21: Super capacitor charging characteristics                                                |

|------------------------------------------------------------------------------------------------------|

| Figure 3.22: Super capacitors used for the experiment                                                |

| Figure 3.23: Test setup for monitoring super capacitor charging                                      |

| Figure 3.24: Super capacitor charging waveform                                                       |

| Figure 3.25: Super capacitor constant current discharging model in MATLAB35                          |

| Figure 3.26: Super capacitor constant current discharging monitored through MATLAB36                 |

| Figure 3.27: Super capacitor voltage vs time at constant current discharge37                         |

| Figure 3.28: Conventional capacitor charging MATLAB model                                            |

| Figure 3.29: Conventional capacitor charging characteristics                                         |

| Figure 4.1: DVR MATLAB model for testing battery storage                                             |

| Figure 4.2: Variation of minimum battery voltage vs time to compensate sags41                        |

| Figure 4.3: SOC of battery at the end of sag vs time                                                 |

| Figure 4.4: Variation of SOC of battery with time during 50% sag                                     |

| Figure 4.5: Voltage at source side during 50% sag condition                                          |

| Figure 4.6: Voltage at sensitive load side at 50% sag condition                                      |

| Figure 4.7: Mean power variation of the battery                                                      |

| Figure 4.8: Variation of SOC of the battery with time under 30% swell                                |

| Figure 4.9: testing the DVR MATLAB model for super capacitor                                         |

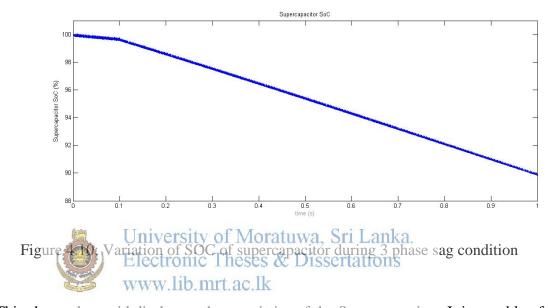

| Figure 4.10: Variation of BOCOTS tipercupation aliting a phase sag condition                         |

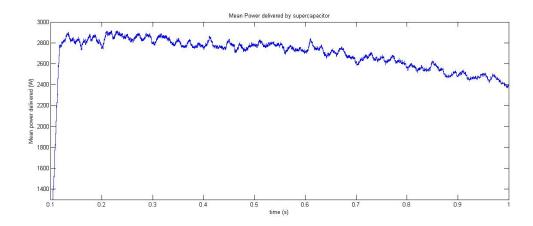

| Figure 4.1 Mean Power variation of Super capacitor disagrant 10115 47                                |

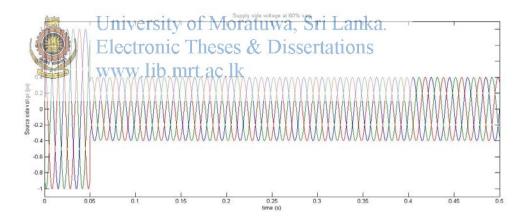

| Figure 4.12: Vottage at source side during 3 phase 60% sag condition                                 |

| Figure 4.13: Voltage at sensitive load side for 0.1F super capacitor at initial voltage of 160V      |

| during 60% sag                                                                                       |

| Figure 4.14: Voltage at sensitive load side for 0.25F super capacitor at initial voltage of 160V     |

| during 60% sag                                                                                       |

| Figure 4.15: Voltage at sensitive load side for 1F super capacitor at initial voltage of 160V during |

| 60% sag                                                                                              |

| Figure 4.16: Variation of Capacitance of supercapaciotor vs duration of sag compensating             |

| capability50                                                                                         |

| Figure 4.17: THD of the injected voltage at the primary side of the injection transformer for        |

| battery storage51                                                                                    |

| Figure 4.18: THD of the injected voltage at the primary side of the injection transformer for super  |

| capacitor storage                                                                                    |

| Figure 4.19: THD of the injected voltage at the primary side of the injection transformer for 0.1F   |

| super capacitor53                                                                                    |

| Figure 4.20: THD of the injected voltage at the primary side of the injection transformer for 1F     |

| super capacitor 53                                                                                   |

| Figure 4.21: THD of the injected voltage at the primary side of the injection transformer vs.     |     |

|---------------------------------------------------------------------------------------------------|-----|

| capacitance of the super capacitor                                                                | 54  |

| Figure 4.22: DVR MATLAB model with Conventional capacitor storage                                 | 55  |

| Figure 4.23: SOC of super capacitor under 40% sag condition for 0.45s duration                    | 56  |

| Figure 4.24: SOC of electrolytic capacitor under 40% sag condition for 0.45s duration             | 56  |

| Figure 4.25: THD level of the injected voltage at the primary side of the injection transformer f | for |

| conventional capacitor storage                                                                    | 57  |

| Figure 4.26: THD level of the injected voltage at the primary side of the injection transformer f | for |

| super capacitor storage                                                                           | 57  |

| Figure 6.1: Hybrid energy storage proposed for DVR                                                | 63  |

# LIST OF TABLES

| Table 1.1: Definitions of Voltage Magnitude Events as used in IEEE Std. 1159-1995               | 1   |

|-------------------------------------------------------------------------------------------------|-----|

| Table 3.1: Super capacitor terminal voltage variation with time at constant current charging    | .34 |

| Table 3.2: Super capacitor terminal voltage variation with time at constant current discharging | 36  |

| Table 4.1: Minimum Battery voltage required to compensate three phase to ground faults          | .40 |

| Table 4.2: Minimum Battery voltage required to compensate single phase to ground faults         | .40 |

| Table 4.3: SOC of the battery with time under 30% swell                                         | .44 |

| Table 4.4: Mean power released by the battery and super capacitor with different sag levels     | .45 |

| Table 4.5: Duration of sag compensating capability with super capacitor Capacitance             | .49 |

| Table 4.6: Variation of THD for 10 cycles of the injected voltage at the primary side of the    |     |

| injection transformer for capacitance of the super capacitor                                    | .54 |

| Table 5.1: Cost comparison for energy storage options                                           | .60 |

| Table 5.2: Variation of energy density and total mass required for energy storage options       | .60 |

| Table 5.3: Required volume of energy storage options                                            | .60 |

| Table 5.4: Variation of power density and total mass required for energy storage options        | .61 |

| Table 5.5: Cycle durability of energy storage ontions                                           | 61  |

#### LIST OF ABBREVIATIONS

Abbreviation Description

rms root mean square

SCR Silicon Controlled Rectifiers

DSTATCOM Distribution Static Synchronous Compensators

SETC Static Electronic Tap Changers

UPS Static Electronic Tap Changers

DVR Dynamic Voltage Restorers

MV Medium Voltage

LV Low Voltage

DC Direct Current

PWM Pulse Width Modulation

VSC Voltage Source Converter

University of Total Canada, Strathtions

Electropoid Flage to Ground Fault Lanka.

HEV Hybrid Electric vehicles

SoC Status of Charge

ESR Equivalent Series Resistance

EPR Equivalent Parallel Resistance

IGBT Insulated Gate Bipolar Junction Transistors

VSI Voltage Source Inverter

Ni-MH Nickel Metal Hydride

THD Total Harmonic Distortion

FFT Fast Fourier Transform

#### 1.0 INTRODUCTION

#### 1.1 Power Quality of Distribution Network

Power distribution network experiences wide range of different disturbances such as voltage sags, swells harmonic distortion, flickers, interruptions, etc.... Among these issues, voltage sags can occur at any instant of time with amplitude ranging from 10% to 90%. Duration of such voltage sags may last for 0.5 cycles to 1 minute. On the other hand sudden increases in the rms voltage or current which are called voltage swells may last for a same duration. But they are less common than voltage sags. Both the voltage sags and swells may affect the sensitive equipment in the distribution network to fail, shutdown or creation of large currents which make the trip the breakers or fuse blow.

Table 1.1: Definitions of Voltage Magnitude Events as used in IEEE Std. 1159-1995

| Voltage range | Iniversity of Moratuwa Sri Lanka. |               |               |

|---------------|-----------------------------------|---------------|---------------|

|               | 0-0.5 cycle<br>www.lib.mrt.ac.lk  | 0.5cycle-1min | >1 min        |

| 10-90%        | Notch                             | Voltage Sag   | Under Voltage |

| 90-110%       | Normal Operating Range            |               |               |

| >110%         | Transient                         | Swell         | Overvoltage   |

#### 1.2 Mitigating the Power Quality Issues

Different voltage regulation strategies are used to solve the above power quality problems. There are two approaches to achieve these voltage regulation. They are controlling the power quality from Customer side or Utility side. Regulating the power quality from customer side is called load conditioning. Regulating the power quality from utility side is called line conditioning. Presently line conditioning systems or utility side solutions play a major role in improving the power quality as well as the customer satisfaction.

Most of the traditional utility side solutions are Transformer with voltage control, Tap changers both mechanical and SCR switched units, servo-variac technology and ferroresonant transformers, etc... But most of these devices are bulky and less efficient.

With the development of Power Electronics, various custom power devices such as Distribution Static Synchronous Compensators (DSTATCOM), Solid State Fault Current Limiter, Static Electronic Tap Changers (SETC), Uninterruptible Power Supplies (UPS), and Dynamic Voltage Restorers (DVRs) have been introduced [1]. But most of those solutions are not economical to a developing country like Sri Lanka as a utility side solution. But the Dynamic Voltage Restorer can be effectively and economically used for voltage regulation as well as mitigating the other power quality problems.

A DVR employ a series of voltage boost technology using solid state switches for compensation of voltage sags/swells. The main function of the DVR is the protection of sensitive loads from such kind of voltage sags/swells. It could be normally installed in a distribution system either at Medium Voltage (MV) or Low Voltage (LV). However DVR installationated vide has some advantages the DVR can be targeted more specifically at Voltage sags sensitive loads. Some that the DVR is easier to protect. Since most of the consumers are at LV level DVR can be installed either by utility or Consumer.

DVR can be installed in the distribution side with no Energy storage or with an Energy storage. DVR topologies without having an Energy Storage have to rely on a dedicated grid connected or distribution transformer connected healthy line. This line provides the energy required for DVR to be released in a voltage disturbance. A shunt converter will convert this energy to feed the DVR. However, the reliability this source of supply should continuously maintained even during a disturbance. Therefore maintaining DVR with no Energy storage is not so economical. Therefore DVRs with a DC energy storages are more precisely used in voltage disturbances. Several DC energy storage systems are used with DVR such as Fly wheels, lead acid batteries, superconducting Magnetic Energy Storage, Fuel Cells, Conventional Capacitor banks, Super capacitors, etc... The performance, economics and sizing of DVR will depend upon this DC energy storage. Therefore a techno-economic study of DVR with Different Energy Storage Systems is important from the perspective of utility as well as the consumers. Also Energy Storage technologies in the world are being rapidly developed. So that

the study of the efficient and economical way of utilizing them for improving the distribution system in Sri Lanka is worthwhile for an Electrical Engineer employed in a Distribution Division in Ceylon Electricity Board.

#### 1.3 Objective of the study

The ultimate objective of this study to investigate the response of a DVR in the presence of Battery Storage, Conventional Capacitor storage and Super capacitor energy storage in compensating the voltages at Low Voltage distribution level and compare the same with economic point of view.

#### 1.4 Scope of the Study

The Scope of this study is mainly to analyze the performance of dynamic Voltage Restorer installed in the Distribution network with different Energy Storage Options. Most common energy istorages in Sylonantay Battery Lstorage and Conventional Capacitor storage are discussed here in conjunction with DVR. Beside this, new and emerging technology of Super capacitor which is still a guest to Sri Lanka, is discussed here. Based on these three energy storages, performance of DVR is analyzed through the following aspects.

- Study of DVR with Generic DC Energy Storage

- Study of Battery Storage, Conventional Capacitor storage and Super capacitor storage

- Designing the DVR computer model

- Designing the Super capacitor computer model

- Energy Storage computer Model verification

- Interfacing the Energy Storages with DVR

- Analysis the response of DVR in a voltage fluctuation for the three energy storage options

- Economic analysis of energy options in conjunction with DVR

#### 1.5 Literature review

Reference [1] addresses on the power quality problems which effect on sensitive loads discussed in this study and it highlights the significance of Dynamic Voltage Restorer among the other custom power devices. Energy requirement for the DVR analyzed in this study is fulfilled through stored energy. Importance of adding energy storage to power electronic compensators are discussed in the reference [2]. Reference [3] describes the most common DC energy storage schemes used for a DVR system. This study considered only three of them which are more common. Characteristics of that three energy storage options mentioned in the same reference are analyzed in this study. Reference [4] explains the conventional system configuration of a DVR and its operating modes which is discussed in this study. Reference [5] suggests two control techniques for detecting and compensating sag/swell conditions which are PI Controller (PI) and Fuzzy Logic Controller (FL). The controller used in this study is based on the PI controller and the same controller tuning settings, LC filter settings and series transformer settings were used and the sensitive load settings were selected from an Indonesian study. Reference of discuss about the super capacitor technology and how the computer models are validated through practical tests. They were useful in determining the tests for validating the proposed model in this study. Reference [7] is focused on integration of DVR with Super capacitor. This provides important information on charging and discharging characteristics of super capacitor. The capability of capacitors in the compensation of sags and swells when integrated with DVR is discussed in Reference [8]. This was useful in testing the variation of sag mitigating capability with capacitance in the system. Reference [9] describes the characteristics and importance of each element of DVR. Elements of the suggested DVR model in this study were designed based on those characteristics.

# 2.0 STUDY OF THE DYNAMIC VOLTAGE RESTORER AND DC ENERGY STORAGE

#### 2.1 Locating the DVR for line conditioning

DVR could be installed either in MV side or LV side. If it is installed in LV side, it should be located between the sensitive load and the point of common coupling (PCC). This will ensure the power quality level of distribution level customers. On the other hand energy storage requirement, installation cost will be minimum for this arrangement and maintenance is much easier.

Installation of DVR in MV side will be required in certain situations where protection of distribution transformers and other MV equipment is required.

Figure 2.2: Location of DVR in MV side

#### 2.2 Equation Related to DVR

Figure 2.3: Circuit Model of DVR installed in a line

When the system voltage  $(V_S)$  drops, the DVR injects a series voltage  $V_{DVR}$  through the injection transformer, so that the desired load voltage magnitude  $V_L$  can be maintained [5]. The series injected voltage of the DVR can be written as

$V_{DVR} = V_L + Z_{Line}I_L - V_s$

Where

V<sub>L</sub>: The desired load voltage magnitude

Z<sub>Line</sub>: The line impedance.

University of Moratuwa, Sri Lanka.

IL: The load carrent Electronic Theses & Dissertations

Vs: The system voltage during fault condition

When  $V_L$  is considered as a reference, equation can be rewritten as,  $V_{DVR} \angle \propto = V_L \angle 0 + I_L Z_{Line} \angle (\beta - \theta) - V_s \angle \delta$

$\propto$ ,  $\beta$ ,  $\delta$  are angles of  $V_{DVR}$ ,  $Z_{Line}$  and  $V_s$  respectively and  $\theta$  is Load power angle

The complex power injection of the DVR can be written as,

$S_{DVR} = V_{DVR}I_L^*$

DVR can absorb or generate reactive power, but active power injection must be provided by an external energy source. The reactive power is generated by converting part of the real power supplied, into reactive power (by the reactive components used in the DVR).

#### 2.3 Conventional System of DVR

The basic operating principle of the Dynamic Voltage Restorer is to inject an appropriate voltage in series with the supply through injection transformer whenever

voltage sag or voltage swell is detected. DVR is located on approach of sensitive loads. If a fault occurs on other lines, DVR insert series voltage and compensates load voltage to pre-fault value. Any differential voltage caused by the disturbances in the distribution feeders will be compensated by an equivalent value generated by the voltage source converters there and injected through the booster transformer. Simplified block diagram to demonstrate this operation is given bellow.

Figure 2.4: Simplified block demonstration of DVR

#### 2.4 Basic elements of DVR

The generic model of a DVR consist of following important elements

- I. Series booster/injection transformer

- II. Passive filter

- III. Voltage Source Converter (VSC)

- IV. Control and voltage injection scheme

- V. DC energy storage with charging mechanism

#### 2.4.1 Series booster/injection transformer

A booster/injection transformer is specially designed to limit the coupling of noise and transient energy from the primary side to the secondary side. It connects the DVR the distribution network via the High Voltage (HV) windings and transformers and couples the injected compensating voltages generated by the voltage source converters to the incoming supply voltage. Further it serves the purpose of isolating the load from the DVR system. Transformer winding ratio is pre-determined according to the voltage requirement of the secondary side. Normally a higher transformer winding ratio is not maintained since it will increase the primary side current which will adversely affect the performance of the power electronic devices such as voltage source converter. Three phase voltage injection transformers are used for this purpose but single phase transformers can be used to inject the compensating voltages separately.

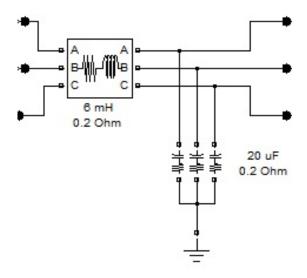

#### 2.4.2 Passive filter

University of Moratuwa, Sri Lanka.

Basically passive filter consist of inductor (L) and capacitor (C). These LC filters are located at the output of the voltage source converter (VSC) to convert the inverted Pulse width modulated (PWM) waveform into a sinusoidal waveform. This is achieved by eliminating the unnecessary harmonic components generated by the VSC. Since higher order harmonic components distort the compensated output voltage, they should be removed from the injected voltage waveform in order to maintain acceptable total harmonic distortion (THD) levels. Generally switching frequencies of the Voltage source converters are maintained at several kHz for medium power levels. Passive filter is placed at the low voltage side of the series injection transformer because when it is placed closer to the harmonic source, higher order harmonic currents are avoided to penetrate into the series injection transformer. It will have the disadvantage of circulating harmonic currents into the transformer, if it is placed on the high voltage side.

Figure 2.5: Passive LC filter

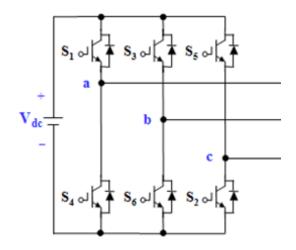

# 2.4.3 Voltage Source Converter

University of Moratuwa, Sri Lanka.

Function of the converted of the converted by the storage device into AC voltage. Generally pulse width modulated voltage source inverters are used for this with a low voltage rating. Typical power electronic six pulse voltage source converter is given below.

Figure 2.6: Six pulse Voltage Source Converter

# 2.4.4 Control and Voltage injection Scheme

Several techniques are used to implement the control scheme of DVR. The control system measures the rms voltage at the load point. It can detect a voltage sag information like starting point, end point and depth by appropriate real-time detection algorithms. Control strategies may be linear or Non-linear. Feedback control strategy is linear control mechanism. It measures the load voltage and difference between the voltage reference of the load and actual load voltage and accordingly, required voltage is injected. Nonlinear control strategies are used whenever the system is unstable and the linear models fail to work properly.

Voltage injection or compensation methods by means of a DVR depend upon the limiting factors such as; DVR power ratings, various conditions of load, and different types of voltage sags. Some loads are sensitive towards phase angel jump and some are sensitive towards change in magnitude and others are tolerant to these. Therefore the control strategies depend sipon the type of load characteristics.

There are interent methods of by the stage injection which are www.lib.mrt.ac.lk

- i. Pre-sag compensation method

- ii. In-phase compensation method

- iii. Reactive power compensation

#### Pre-sag compensation method

In Pre-Sag compensation, it is important for both magnitude and the phase angle to be compensated. The different between the pre-sag and during the sag voltage are detected by the DVR and it injects the different voltage, Therefore, the amplitude and the phase of the voltage before the sag has to be exactly restored

#### *In- Phase Compensation:*

In-Phase Compensation technique, the injection voltage is in phase with the source. When the source voltage is drop due to sagging problems in the network the injection voltage produced by the Voltage Source Inverter (VSI) will injects the missing voltage based on the drop voltage magnitude.

#### Reactive power compensation

In the reactive power compensation only a small energy storage is required and hence not require any active power. In this technique, the injected voltage is in quadrature with the load current.

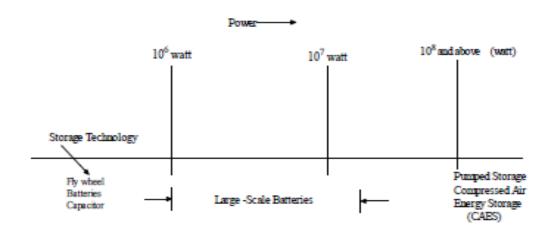

#### 2.4.5 DC Energy Storage with charging mechanism

The purpose of a DC Energy Storage is to supply the necessary energy to the VSC via a dc link for the generation of injected voltages.

Energy storage devices are divided into three categories:

- i. Small categories (<10MW): Flywheels, batteries, capacitors, ultra capacitors.

- ii. Medium categories (10MW < energy < 100 MW): Large-scale batteries.

- iii. Large categories (≥ 100 MW). Pumped storage, compressed air energy storage (CAES) University of Moratuwa, Sri Lanka.

Electronic Theses & Dissertations

Technical capabilities of the above energy storage options can be classified as demonstrated in the below figure [3].

Figure 2.7: Technical capabilities of the energy storage options

Energy and power density of the Battery, Super capacitor and conventional capacitor storage can be compared by the figure 2.8

Figure 2.8: Power and Energy Density of Storage options

Since this study of DVR is carried out for DVR installed in the LV side, only the small scale energy storages Battery, Conventional Capacitors and Ultra Capacitors which are used in Sri Lanka were considered. Among these energy storage options, this study is more focused on super capacitor energy storage which is still new to Sri Lanka.

#### Battery Energy Storage

Batteries redectrochemical devices which converts the energy into electrical energy during discharge time. The total energy stored and the weight of the battery unit is considered to be important technological aspects, another important factor is the cost of the batteries. The total energy that can be stored in a battery usually follows the weight and volume more or less linearly. The linear factors are called "specific energy" (Wh/kg) and "energy density" (Wh/l). The highest power a battery can deliver is also limited and is, similar to energy, measured in "specific power" (W/kg) and "power density" (W/l). There are a number of different battery types on the market today, some of them more established and some more new and modern. For high power application there are two major technologies of interest, namely the NiMH and the Li-Ion.

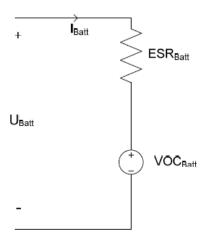

The equivalent electrical model of a battery is given in the figure 2.9.

Figure 2.9: Equivalent Electrical Model of a Battery

The ESR<sub>Batt</sub> is the equivalent series resistance and the open circuit voltage is labeled VOC<sub>Batt</sub>. The value of the components depends on temperature, state of Charge (SoC) and the current. The output voltage will drop with increasing power output and rise with power input due to the voltage drop over the resistor. Also, the power dissipated in the resistor is thermal losses. Typical discharge curve of a battery is indicated in the figure 2.10.

Figure 2.10: Typical Discharge Characteristics of Battery Storage

#### Conventional Capacitor Energy Storage

In its basic form, a Capacitor consists of two or more parallel conductive (metal) plates which are not connected or touching each other, but are electrically separated either by air or by some form of a good insulating material such as waxed paper, mica, ceramic, plastic or some form of a liquid gel as used in electrolytic capacitors. The insulating layer between a capacitors plates is commonly called the Dielectric. Due to this insulating layer, DC current cannot flow through the capacitor as it blocks it allowing instead a voltage to be present across the plates in the form of an electrical

charge. The conductive metal plates of a capacitor can be either square, circular or rectangular, or they can be of a cylindrical or spherical shape with the general shape, size and construction of a parallel plate capacitor depending on its application and voltage rating.

Figure 2.11: Structure of a Conventional Capacitor

Figure 2.12: Charging and discharging characteristics of conventional capacitor

#### Super capacitor Energy Storage

A super capacitor is a component which has relatively high specific power ability in comparison to batteries much like a capacitor, while it has much higher specific energy than a conventional capacitor, more like a battery. The main difference between the

super capacitor and the ordinary electrostatic capacitor is that the electrolyte in the super capacitor contains free charges in the form of ions. The ordinary capacitor does not have this type of free charges. In a traditional electrostatic capacitor the electrodes consist of a thin surface on which the charges are gathered. In a super capacitor the electrodes consist of a porous micro structure illustrated in the figure 2.13.

The Super capacitor that can be made of carbon material and around it the electrolyte is deposited. This structure gives a significantly larger specific surface area than the electrostatic capacitors have. To separate anode and cathode a thin isolation membrane is located between the electrodes of the super capacitor. Due to this thin isolator in super capacitors, the maximum voltage per cell becomes relatively low, in order of 2-4V to avoid dielectric breakdown.

When the super capacitor is charged, the electrons at the cathode attract positive ions and on the anode the vacancies for electrons attract negative ions in order to locally obtain a charged balance. This attraction of ions leads to a capacitance being formed between the ions and the surface of the electrode. The name dual layer comes from the two layers of ions at each electrode. The layer closest to the electrode acts as a dielectric and the layer outside the first layer holds the charges. This occurs at both electrodes in the super capacitor and the total capacitance consists of these two

capacitances connected in series. When charges attract ions, they are gathered at the electrode surface. This effect has been illustrated in the figure 2.14.

Figure 2.14: Structure of Uncharged and Charged Super capacitor

There are a number of different ways to model the electric properties of a super capacitor. Most common simplified model is given in the figure 2.15, where C<sub>0</sub> denotes the nominal capacitance, which is dependent on the open circuit voltage. ESR is the equivalent series resistance, which is the main contributor to losses. EPR is the University of Moratuwa, Sri Lanka. equivalent parallel resistance, which is there to model self-discharge. Generally ESR is in the range of milli-ohms and EPR is in the range of kilo-ohms.

Figure 2.15: Equivalent Electrical Model of a Super capacitor

Beside the model illustrated in the figure 2.15, there are many other models which consists of several RC branches for different time duration responses. However, for the purpose of comparing the response of DVR for Super capacitor with other energy storage options, this model is adequate.

Further charging and discharging characteristics of super capacitor at constant current levels are illustrated in the figure 2.16

Figure 2.16: Charging and discharging characteristics of Super capacitor

#### 3.0 RESEARCH METHODOLOGY

# 3.1 Modelling the MV and LV distribution feeders

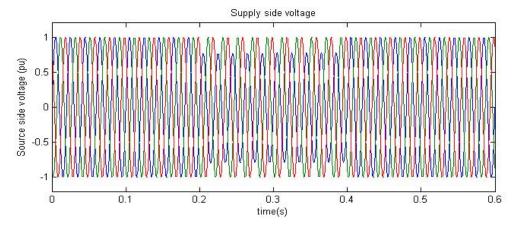

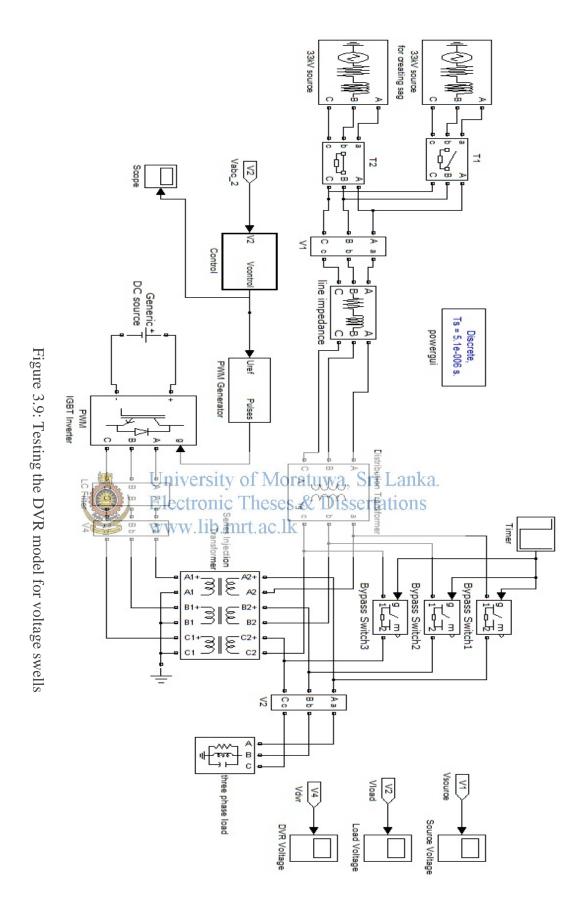

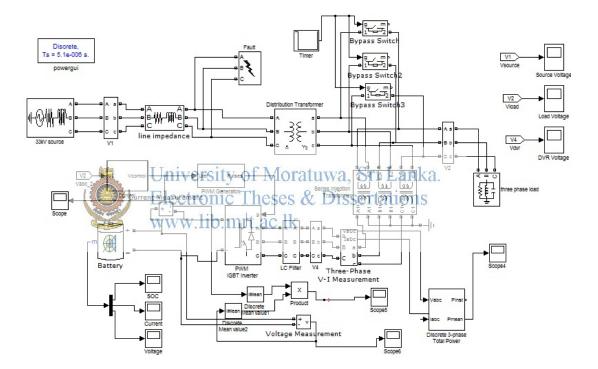

In order to simulate the function of a DVR in a power quality issue in a distribution line, computer models of the MV and LV distribution feeders and the DVR were setup. MATLAB R2008b Simulink was used for this simulation. Since the DVR was located at the LV side, Medium Voltage power system and the downstream were modelled. 33kV feeder bay was modelled as a 33kV generating source. To create a sudden voltage sag event, Fault block in the Simulink package was used and to create sudden swell, source voltage was boosted. A bypass switch was connected through injection transformer in order to set the DVR in the standby mode when it is not injecting power. Source voltage and load voltages before and after the sag event and during the sag event were monitored using scopes. In addition, voltage injection in the sag event was monitored using another scope.

#### 3.1.1 Modeling the 33kV Feeder bay and the MV line

A lynx conductor feeder emanating from Horana Grid Substation was selected for the model where the distribution transformer was located 10km away from the Grid Substation. Following parameters of the 33kV Generation source were added in the model

- Phase to phase voltage and frequency=33kV, 50Hz

- Three phase short circuit level =463MVA

- Internal connection=Y<sub>g</sub>

- X/R ratio=10

In addition, following feeder parameters were selected

• Feeder parameters R=1.78 $\Omega$ , L=0.01035 H (for 10km length)

#### 3.1.2 Modeling the Distribution Transformer

Following parameters of the Distribution transformer was used for the model

Vector Group=Dyn11

- Nominal power and frequency=160MVA, 50Hz

- Primary Winding Voltage=33kV

- Primary Winding R (pu)=0.0001

- Primary Winding x (pu)=0.045

- Secondary Winding Voltage=400V

- Secondary Winding R (pu)=0.0001

- Secondary Winding X (pu)=0.045

#### 3.1.3 Modelling the sensitive load

- Configuration= Y

- Active Power=2kW

- Line Voltage and frequency=400V,50Hz

# 3.1.4 Creating the Voltage Sag and Swell

Fault block in the Simulink package was used for creating single phase and three phase sags for desired time durations. A voltage boosted source block was applied to source Electronic Theses & Dissertations side in order to create a swell.

- Fault resistance= $4.6\Omega$

- Ground resistance= $0.1\Omega$

% sag was determined using the equation

$$Sag=Z_s/(Z_s+Z_f)$$

Z<sub>s</sub>-Source Impedance

Z<sub>f</sub>-Fault Impedance

Swell=Voltage boost/rated voltage

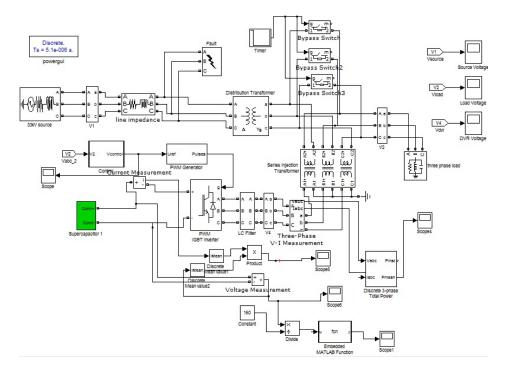

# 3.2 Modelling the DVR

Basic models in the Simulink package was used for the elements of DVR. The Generic DC voltage source model was used for DVR energy storage for testing the model.

# 3.2.1 Modeling the Series Injection Transformer

Three phase rated power= 15 kVA

Winding 2: Winding 1 ratio=1000:100

# **3.2.2** Modeling the IGBT converter

Number of bridge arms=3

fall time  $(T_f)=1\mu s$

tail time  $(T_t)=2\mu s$

$R_{ON} = 0.0001\Omega$

#### 3.2.3 Modelling the LC filter

Series RL Branch

$R=0.2\Omega$

L=6mH

$R=0.2\Omega$

Shunt RC Branch University of Moratuwa, Sri Lanka. Electronic Theses & Dissertations www.lib.mrt.ac.lk

C=20µF

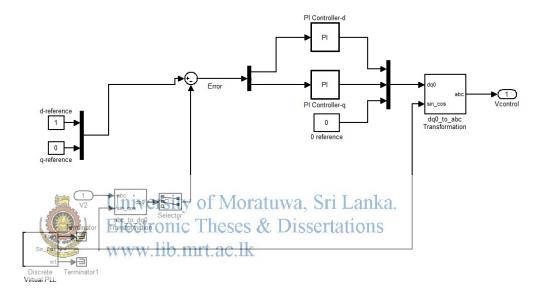

#### 3.2.4 Modelling the control system

The input signal for the control unit was obtained from the voltage, V2 measured by three-phase V-I measurement at the sensitive load in per unit values. V2 was then transformed to dq term using the following abc to dq0 transformation matrix.

$$\begin{bmatrix} u_d \\ u_q \\ u_0 \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos(\theta) & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ -\sin(\theta) & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix}$$

A selector switch was used to select only the d and q channels. The voltage sag was detected by measuring the error between the dq-voltage and the reference values. The d-reference was set to rated voltage and q-reference is set to zero. The dq components of load voltage were compared with the reference values and the error signal was sent to PI controller. Two PI controller blocks were used for amplifying and tuning up the error signal-d and error signal-q separately. For error signal-d, KP gain value was set to 40 and  $K_i$  gain value was set to 154. For error signal-q,  $K_P$  and  $K_i$  was set to 25 and 260 respectively [5]. Finally the outputs of the PI controller were transformed back into  $V_{abc}$  using the following transformation matrix and forwarded to PWM generator

$$\begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix} = \begin{bmatrix} \cos(\theta) & -\sin(\theta) & 1 \\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) & 1 \\ \cos(\theta + \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) & 1 \end{bmatrix} \begin{bmatrix} u_d \\ u_q \\ u_o \end{bmatrix}$$

Discrete Virtual Phase lock loop (PLL) was used as a phase reference signal for input and output signal which creates a sinusoidal waveform. Control system implemented in MATLAB Simulink is illustrated in the figure 3.1.

Figure 3.1: Control system of DVR

A Discrete Pulse width modulation Generator (PWM) was used for drive the IGBT which has the following parameters

Carrier frequency=10 kHz

Sample time=5µs

# 3.3 Testing the model for voltage compensation

Complete DVR model was tested for three phase to ground faults and single phase to ground faults where it creates sags. Voltage levels at source side, sensitive load side and voltage injected by the DVR was monitored. Fault condition was maintained for 0.2s for monitoring the voltage compensation.

33kV source Vabc\_2 ¥2 Scope 00 < Control Voontro Iine impedance Generic ±

DC source PWM Generator IGBT Inverter Pulses PWM 0 8 > ratuwa, Sis Lank Fault Stres Injection

Transformer Timer Bypass Switch1 3||€<sup>A2+</sup> Bypass Switch3 Bypass Switch2 + 1 1 m 81+3|E82+ 813|E82 C1+3|EC2+ C13|EC2+ B 6 5 00 three phase load Vsource Vload V2 V4 Vdvr Discrete, Ts = 5.1e-006 s. powergui Source Voltage DVR Voltage Load Voltage

Figure 3.2: Complete DVR model for Sag

# 3.3.1 Testing for Single phase voltage sags

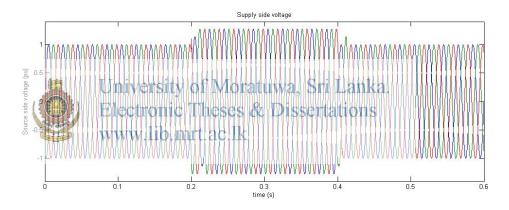

It was observed that under a single phase to ground fault a voltage sag has been appeared at the source side (measurement V1) as in the figure 3.3

Figure 3.3: Voltage measured at Source side for single phase sag

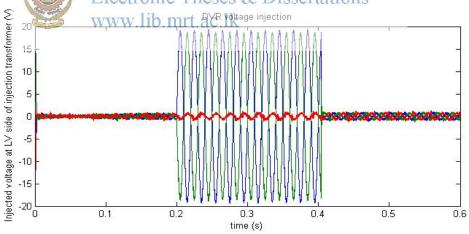

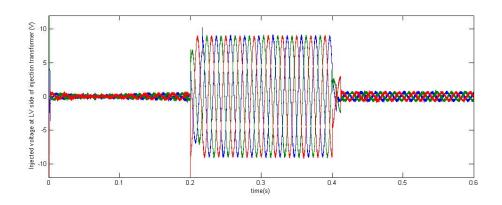

To compensate this voltage sag, DVR injects a voltage (measurement at Vdvr) at the LV side of the injection transformer indicated in the figure 3.4 Electronic Theses & Dissertations

Www.lib.mrt.ave injection

Figure 3.4: Voltage Injected by DVR to Compensate the Sag

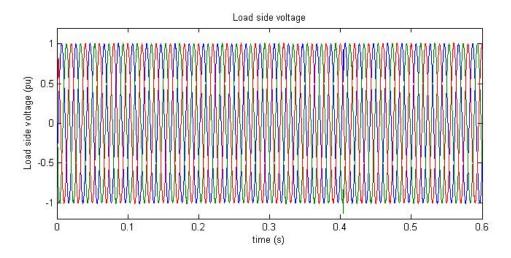

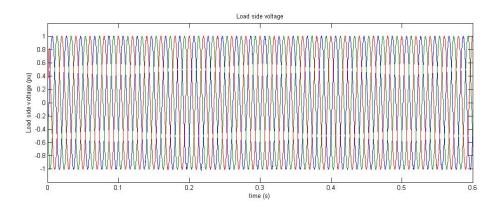

It was noted that the Voltage at the sensitive load side (measurement V2) was not affected by this sag as it has been fully compensated by the DVR as indicated in the figure 3.5

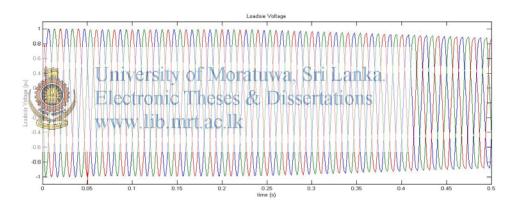

Figure 3.5: Voltage measured at sensitive load side for single phase sag

# 3.3.2 Testing for 3 phase sags

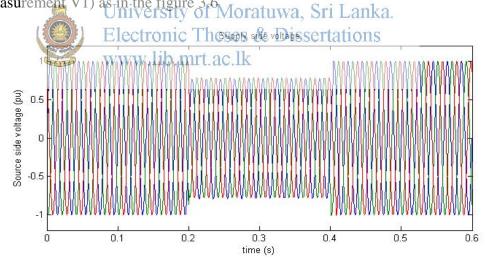

Same test was carried out for a three phase sag condition. It was observed that under a three phase to ground fault a voltage sag has been appeared at the source side (measurement V1) as in the figure 3.6 (acceptance Stri Lanks)

Figure 3.6: Voltage measured at Source side for three phase sag

To compensate this voltage sag, DVR injects a voltage (measurement at Vdvr) at the LV side of the injection transformer indicated in the figure 3.7

Figure 3.7: Voltage Injected by DVR to Compensate the Sag

It was noted that the Voltage at the sensitive load side (measurement V2) was not affected by this sag as it has been fully compensated by the DVR as indicated in the figure 3.8

Figure 3.8: Voltage measured at sensitive load side for three phase sag

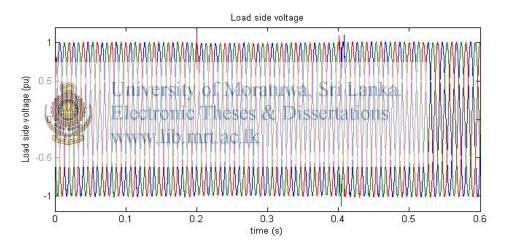

# 3.3.3 Testing for voltage swells

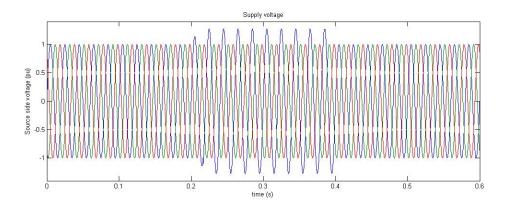

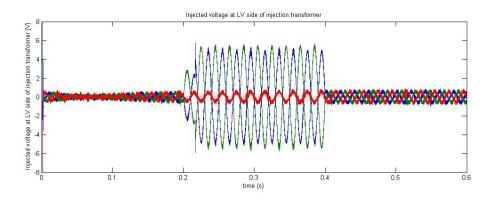

Supply voltage was boosted using an additional three phase voltage source, to create voltage swell at the source side

#### Testing for 1 phase swells

Tests carried out for sag conditions were repeated for swell conditions. A boosted voltage source was connected to the supply side during the swell condition. A single phase swell condition created at the source side was monitored (measurement V1) as in the figure 3.10

Figure 3.10: Voltage measured at Source side for single phase swell

To compensate this voltage swell, DVR injects a voltage (measurement at Vdvr) at the LV side of the injection transformer indicated in the figure 3.11

Figure 3.11: Voltage Injected by DVR to Compensate the Swell

It was noted that the Voltage at the sensitive load side (measurement V2) was not affected by this swell as it has been fully removed by the DVR as indicated in the figure 3.12

Figure 3.12: Voltage measured at sensitive load side for single phase swell

## Testing for 3 phase swells

Same test was carried out for a three phase swell condition. Three phase swell condition was created at the source side (measurement V1) as in the figure 3.13

Figure 3.13: Voltage measured at Source side for three phase swell

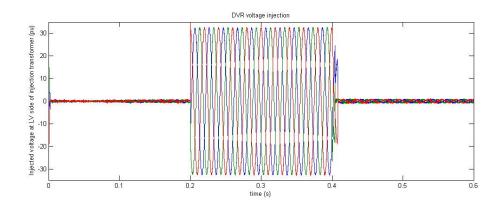

To compensate this voltage swell, DVR injects a voltage (measurement at VDVR) at the LV side of the injection transformer as indicated in the figure 3.14.

Figure 3.14: Voltage Injected by DVR to Compensate the Swell

It was noted that the Voltage at the sensitive load side (measurement V2) was not affected by this swell as it has been fully removed by the DVR as indicated in the figure 3.15.

Figure 3.15: Voltage measured at sensitive load side for single phase swell

3.4 Modeling the DCi Energy Storage for DVR, Sri Lanka.

Electronic Theses & Dissertations

3.4.1 Modeling the Battery Energy Storage

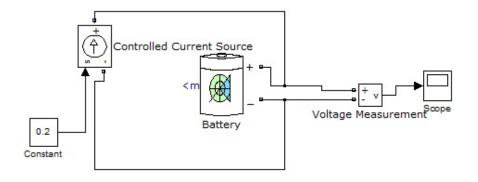

Standard Battery model in MATLAB R2008b was used for the simulation. A 1.2V Nickel Metal Hydride (NiMH) Battery cell model was selected for testing since it has comparatively high energy density and rapid charging is possible. Its charging characteristics were tested by applying a constant current of 0.2A as in the figure 3.16.

Figure 3.16: Testing the charging characteristics of the battery

Accordingly, charging characteristics of battery at constant current was monitored as in the figure 3.17

Figure 3.17: Constant current charging characteristics of battery

University of Moratuwa, Sri Lanka.

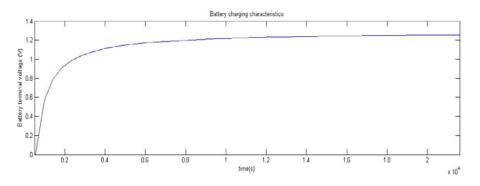

Typical charging characteristics extracted from a NiMH manufacturer's datasheet is as follows (see the figure 3.18). mrt. ac.lk

| Specifications     |                   |

|--------------------|-------------------|

| Diameter           | 17.0 +0 / -0.7 mm |

| Height             | 43.0 +0 / -1.5mm  |

| Approximate Weight | 32g               |

|                    |                   |

| Nominal Voltage               |                      | 1.2V         |                     |

|-------------------------------|----------------------|--------------|---------------------|

| Dis                           | Discharge Average    |              | 2040mAh             |

| Ca                            | pacity*              | Rated (Min.) | 2000mAh             |

| Approx. Internal impedance at |                      | 20mΩ         |                     |

| 1000Hz at charged state.      |                      | 2011122      |                     |

| Charge Standard Rapid         |                      | Standard     | 200mA (0.1C)x 16h   |

|                               |                      | Rapid        | 1700mA (0.85C)x 1.4 |

| Ф                             | Charge               | Standard     | 0°C to 45°C         |

| # h                           | Charge               | Rapid        | 0°C to 40°C         |

| rat                           | <u>ਛ</u> ਇ Discharge |              | -10°C to 65°C       |

| du<br>pe                      |                      | < 1 year     | -20°C to 35°C       |

| Ambient Temperatur Storage    | Storage              | < 3 months   | -20°C to 45°C       |

|                               |                      | < 1 month    | -20°C to 55°C       |

Figure 3.18: Battery charging characteristics manufacturer's data

Therefore the above MATLAB model used for the battery energy storage could be validated.

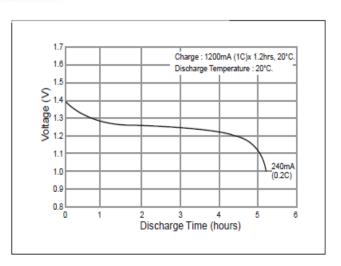

## 3.4.2 Modelling the Super capacitor Energy Storage

Since MATLAB R2008b has no standard models for super capacitor, an equivalent model illustrated in the figure 2.15 was built up using the basic elements as illustrated in the figure 3.19.

Figure 3-19: Supervioration MASL: ABampdel Electronic Theses & Dissertations

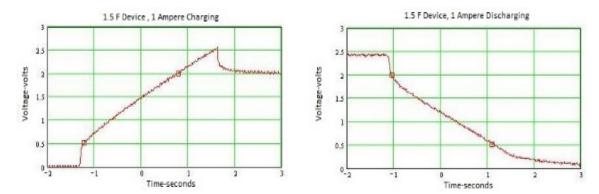

Constant current charging characteristics of super capacitor model was tested by applying a current pulse as in the figure 3.20. Terminal voltage variation was monitored using MATLAB. The parameters of the same super capacitor (see the figure 3.22) which was selected for validating the above model were obtained from manufacturer's datasheet and applied for the MATLAB model.

Test parameters of the Supercapacitor

- Capacitor=9F/3V

- ESR= $0.2 \Omega$

- EPR was selected as  $2.7k\Omega$

Figure 3.20: Testing the super capacitor charging characteristics

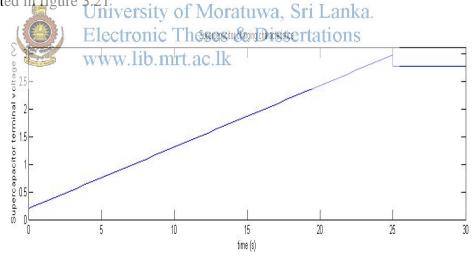

Voltage variation across the terminals of the super capacitor was monitored as illustrated in figure 3.21.

Figure 3.21: Super capacitor charging characteristics

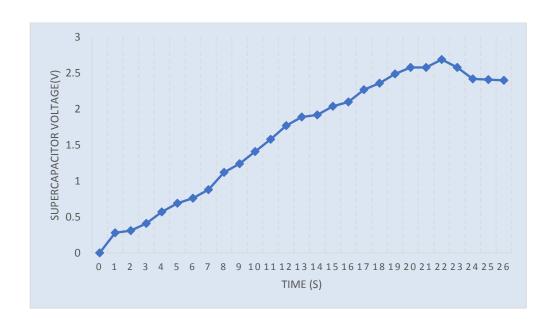

In order to validate the above MATLAB model, the 3V/9F super capacitor was tested in applying a constant current while monitoring its terminal voltage as in the figure 3.23.

Figure 3.22: Super capacitors used for the experiment

Figure 3.23: Test setup for monitoring super capacitor charging

Super capacitor terminal voltage variation with time was recorded as tabulated in the table 3.1.

Table 3.1: Super capacitor terminal voltage variation with time at constant current charging

| time(s)  | Super capacitor voltage(V)           |

|----------|--------------------------------------|

| 0        | 0                                    |

| 1        | 0.28                                 |

| 2        | 0.31                                 |

| 3        | 0.41                                 |

| 4        | 0.57                                 |

| 5        | 0.69                                 |

| 6        | 0.76                                 |

| 7        | 0.88                                 |

| 8        | 1.12                                 |

| 9        | 1.24                                 |

| 10       | 1.41                                 |

| 11       | 1.58                                 |

| 12       | 1.77                                 |

| 13       | 1.89                                 |

| 14       | 1.92                                 |

| Iniversi | y of Morat <del>uwa,</del> Sri Lanka |

| lectroni | c Theses & Dissertations             |

| vww.lib  | mrt.ac.lk 2.27<br>2.36               |

| 19       | 2.49                                 |

| 20       | 2.58                                 |

| 21       | 2.58                                 |

| 22       | 2.69                                 |

| 23       | 2.58                                 |

2.58 23

24

25 26

Super capacitor voltage was plotted against time as illustrated in the figure 3.24

2.42 2.41

2.4

Figure 3.24: Super capacitor charging waveform

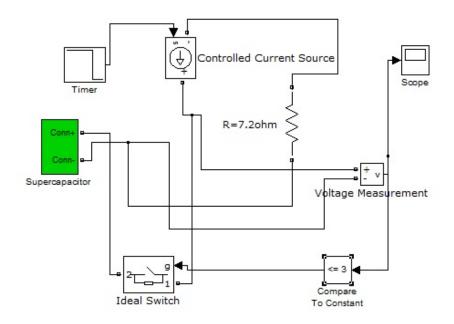

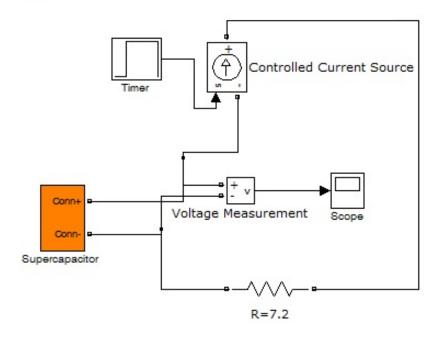

Fully charged supercapacitor was discharged through the  $7.2\Omega$  resistor under a constant current of 1A. The setup was modelled in MATAB as in the figure 3.25

Electronic Theses & Dissertations www.lib.mrt.ac.lk

Figure 3.25: Super capacitor constant current discharging model in MATLAB

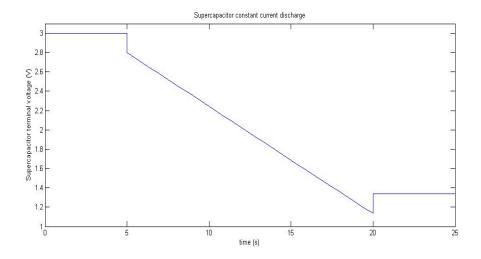

# Following response indicated in the figure 3.26 was observed in MATLAB

Figure 3.26: Super capacitor constant current discharging monitored through MATLAB

Further, 9F/3V super capacitor was charged to its maximum voltage level and it was discharged through  $7.2\Omega$  resistance maintaining 1A current, while monitoring its terminal voltage. Terminal voltage Variation with time was additated as in the table 3.2 Electronic Theses & Dissertations www.lib.mrt.ac.lk

Table 3.2: Super capacitor terminal voltage variation with time at constant current discharging

| time(s) | Super capacitor voltage(V) |

|---------|----------------------------|

| 0       | 2.85                       |

| 1       | 2.85                       |

| 2       | 2.83                       |

| 3       | 2.83                       |

| 4       | 2.81                       |

| 5       | 2.7                        |

| 6       | 2.65                       |

| 7       | 2.62                       |

| 8       | 2.45                       |

| 9       | 2.43                       |

| 10      | 2.21                       |

| 11      | 2.18                       |

| 12      | 2.01                       |

| 13      | 1.97                       |

| 14      | 1.86                       |

| time(s) | Super capacitor voltage(V) |

|---------|----------------------------|

| 15      | 1.75                       |

| 16      | 1.68                       |

| 17      | 1.47                       |

| 18      | 1.31                       |

| 19      | 1.25                       |

| 20      | 1.12                       |

| 21      | 1.26                       |

| 22      | 1.26                       |

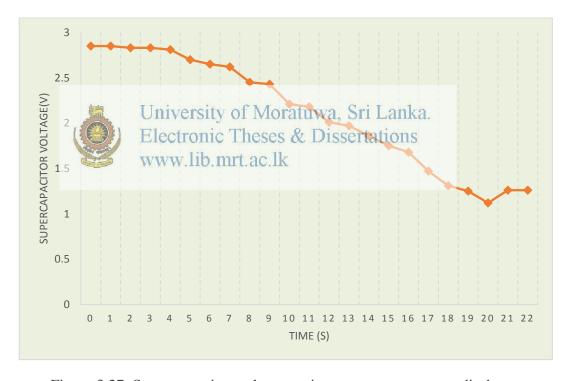

Super capacitor voltage was plotted against time as indicated in the figure 3.27

Figure 3.27: Super capacitor voltage vs time at constant current discharge

Accordingly, it was concluded that the above MATLAB model is equivalent to the characteristics of the real super capacitor selected for the test.

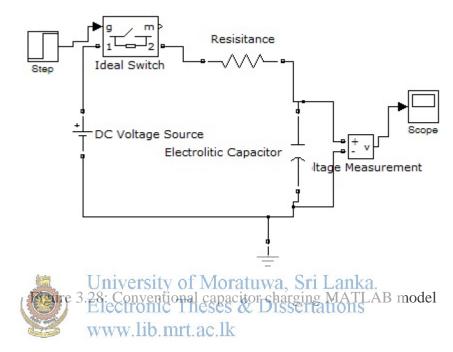

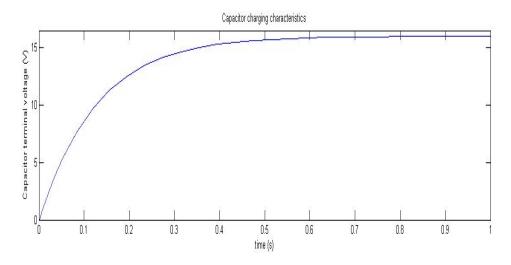

## 3.4.3 Modeling the conventional capacitor Storage

A simple RC (R=2.7k $\Omega$ , C=47 $\mu$ F) network model was modeled in MATLAB and a 16V DC voltage pulse was applied to the circuit and the voltage variation across the capacitor was measured as illustrated in the figure 3.28.

Accordingly, charging characteristics of the conventional capacitor was monitored as indicated in the figure 3.29 which is similar theoretical characteristics.

Figure 3.29: Conventional capacitor charging characteristics

# 4.0 RESULTS AND DISCUSSION

# 4.1 Integration of the battery energy storage with the DVR

Response of DVR with the 2Ah Ni-MH battery storage was tested for different sag conditions in a fixed time duration. Test setup modelled in MATLAB is illustrated in figure 4.1.

Figure 4.1: DVR MATLAB model for testing battery storage

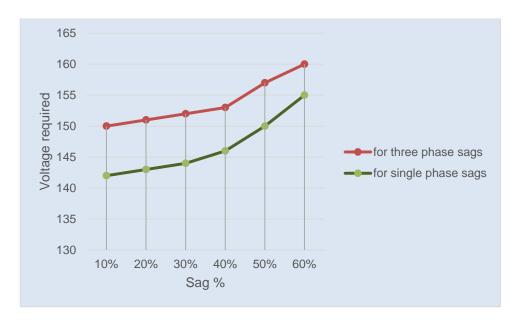

Minimum voltage levels of the battery were checked for single phase to ground fault and three-phase to ground fault conditions. Results are tabulated in the table 4.1 and 4.2.

Table 4.1: Minimum Battery voltage required to compensate three phase to ground faults

| Sag level (%) | Minimum            | Battery(2Ah) | voltage | requited | to |

|---------------|--------------------|--------------|---------|----------|----|

|               | compensate the sag |              |         |          |    |

| 10%           | 150                |              |         |          |    |

| 20%           | 151                |              |         |          |    |

| 30%           | 152                |              |         |          |    |

| 40%           | 153                |              |         |          |    |

| 50%           | 157                |              |         |          |    |

| 60%           | 160                |              |         |          |    |

Table 4.2: Minimum Battery voltage required to compensate single phase to ground faults

| Sag level (%) | Minimum Battery(2Ah) voltage requited to                                           |

|---------------|------------------------------------------------------------------------------------|

| Electr        | reitmpefishtentetsaya, Sri Lanka.  opig Theses & Dissertations  lib mrt.ac.lk  143 |

| 30%           | 144                                                                                |

| 40%           | 146                                                                                |

| 50%           | 150                                                                                |

| 60%           | 155                                                                                |

It was observed that, in order to compensate heavy sags, initial battery voltage should be set to higher amount of voltage thresholds. But for small scale of sags, there is no significant voltage change. The above tabulated results were plotted as indicated in figure 4.2.

Figure 4.2: Variation of minimum battery voltage vs time to compensate sags

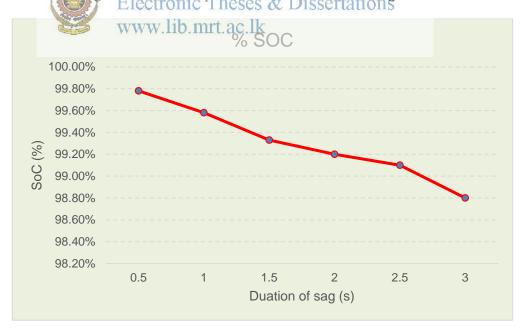

Further, DVR was tested for 100% charged Ni-MH battery for 50% constant sag level under different sag durations from 0.5 seconds to 3 seconds, the status of charge (SOC) of the battery at the end of the sag duration was monitored. Variation of Battery SoC University of Moratuwa, Sri Lanka. with different sag durations were plotted as illustrated in the figure 4.3.

Figure 4.3: SOC of battery at the end of sag vs time

It was found that there is no considerable variation in the SOC. This indicates that battery is releasing its charge to the converter in a slower manner.

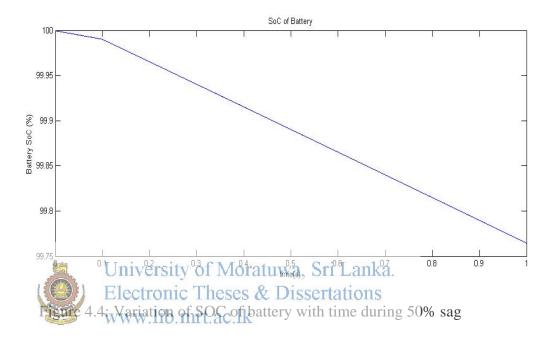

This situation was well monitored using the scope connected to monitor the status of charge with time as illustrated in figure 4.4. It was observed that even for a 50% sag, at the end of sag condition at 1s, the battery SOC was reduced only by 0.24%. It means charges were released to the VSC from the battery in a very slower manner. This is because of low power discharge efficiency of the battery storage.

The 50% sag condition created at the supply side is indicated in figure 4.5

Figure 4.5: Voltage at source side during 50% sag condition

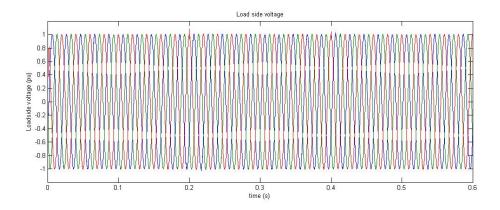

However it was observed that the sag has been successfully compensated for the whole duration (see the figure 4.6)

Figure 4.6: Voltage at sensitive load side at 50% sag condition

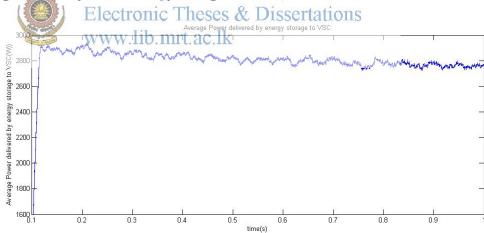

Mean power delivered through the battery during the sag condition was monitored (see the figure 4.7) and noticed that the battery can maintain the power delivery to the converter in nearly constant manner during sag condition. This is because of the low discharge efficiency of the battery of orageratuwa, Sri Lanka.

Figure 4.7: Mean power variation of the battery

Same observations were there for the three phase voltage swell. DVR was tested for 100% charged Ni-MH battery for 30% voltage swell level under different durations from 0.5 seconds to 3 seconds, the status of charge (SOC) of the battery at the end of the swell duration was monitored. Results were tabulated in the table 4.3.It was found that there is no considerable variation in the SOC.

Table 4.3: SOC of the battery with time under 30% swell

| Duration of the three phase voltage | SOC at the end of swell |

|-------------------------------------|-------------------------|

| swell (s)                           |                         |

| 3                                   | 99.52%                  |

| 2.5                                 | 99.61%                  |

| 2                                   | 99.69%                  |

| 1.5                                 | 99.74%                  |

| 1                                   | 99.91%                  |

| 0.5                                 | 99.95%                  |

Variation of Battery SoC with Sag duration was plotted as illustrated in the figure 4.8

Figure 4.8: Variation of SOC of the battery with time under 30% swell

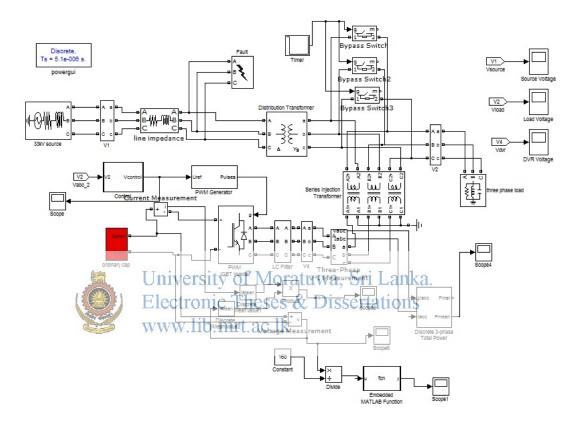

# 4.2 Integration of the super capacitor energy storage with the DVR

Response of DVR with the 3F, 160V super capacitor storage was tested for different sag conditions in a fixed time duration. Test setup modelled in MATLAB is illustrated in the figure 4.9.

Figure 4.9: testing the DVR MATLAB model for super capacitor

To monitor the high energy discharge characteristics of the super capacitor, it was University of Moratuwa, Sri Lanka. connected as the DC storage of DVR and tested the response for three phase sags with variable magnitudes for a fixed duration. Finally it was compared with the response of a same voltage Ni-MH battery. Results were tabulated as indicated in table 4.4.

Table 4.4: Mean power released by the battery and super capacitor with different sag levels

| % Sag | Power released by the | Power released by the Ni- |

|-------|-----------------------|---------------------------|

|       | Super capacitor(W)    | MH battery(W)             |

| 60    | 2050                  | 1500                      |

| 50    | 1870                  | 1490                      |

| 40    | 1850                  | 1465                      |

| 30    | 1850                  | 1465                      |

| 20    | 1850                  | 1440                      |

| 10    | 1850                  | 1440                      |

It was observed that the super capacitor's rate of releasing its power to the VSC is higher than that of a battery because of its high discharging efficiency. Compensating deeper sags, Super capacitor energy can be effectively used than the battery, but in the case of comparatively low sags, they do not show a significant variation in releasing power.

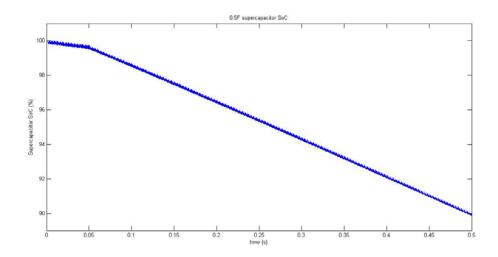

In the figure 4.4 it was observed that 3 phase sag of 50% the SOC of the battery was reduced only by 0.24% at the end of sag at 1s. But under the same initial voltage, a 1F Super capacitor SOC has been reduced approximately by 10% at the end of the sag at 1s which is illustrated in the figure 4.10.

This shows the rapid discharge characteristics of the Super capacitor. It is capable of releasing high amount of power to compensate even deeper sag effectively because of its high power density. However even though it can release power efficiently, it cannot maintain the power levels for longer periods as the battery storage. Figure 4.11 shows that the released mean power level of super capacitor is rapidly reducing with time, while the battery is trying to maintain it at approximately constant level.

Figure 4.11: Mean Power variation of Super capacitor during sag

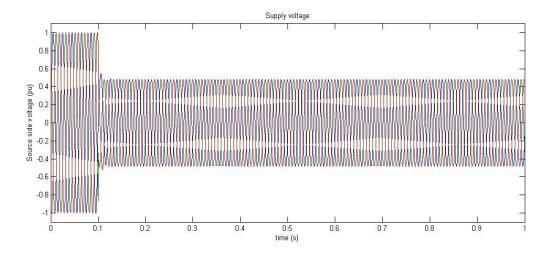

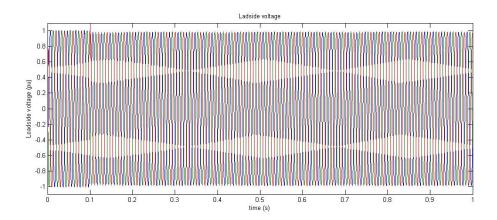

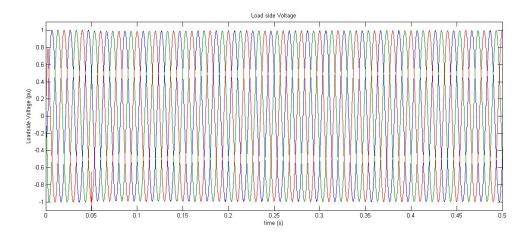

Further, a 60% sag condition was created for 0.45s as illustrated in the figure 4.12 and load side voltage was monitored varying the capacitance of the super capacitor at 160V constant voltage level.

Figure 4.12: Voltage at source side during 3 phase 60% sag condition

Load side voltage for 0.1 F capacitance is indicated in figure 4.13

Figure 4.13: Voltage at sensitive load side for 0.1F super capacitor at initial voltage of 160V during 60% sag

Load side voltage for 0.25 F capacitance is indicated in figure 4.14

Figure 4.14: Voltage at sensitive load side for 0.25F super capacitor at initial voltage of 160V during 60% sag

Load side voltage for 1F capacitance is indicated in figure 4.15. It was observed that sag was completely compensated by 1F capacitance.

Figure 4.15: Voltage at sensitive load side for 1F super capacitor at initial voltage of 160V during 60% sag

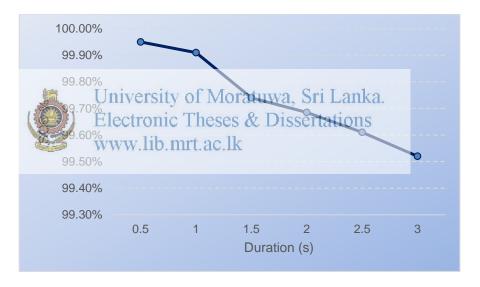

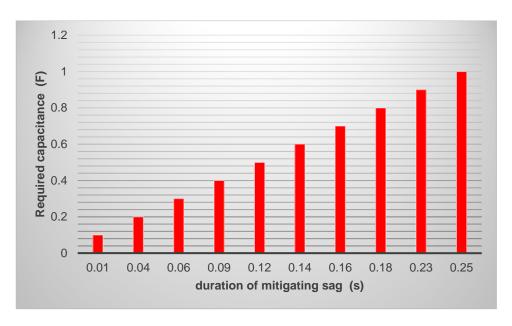

Maximum sag compensating duration for a selected capacitance of super capacitor was monitored by varying the capacitance of the super capacitor storage and testing the response with DVR. Results were tabulated in the table 4.5

University of Moratuwa, Sri Lanka.

Table 4.5t: Transport of Moratuwa, Sri Lanka.

Table 4.5t: Transport of Moratuwa, Sri Lanka.

Www.lib.mrt.ac.lk

| Capacity of the Super | duration of Sag            |

|-----------------------|----------------------------|

| capacitor (F)         | compensating capability(s) |

| 0.1                   | 0.01                       |

| 0.2                   | 0.04                       |

| 0.3                   | 0.06                       |

| 0.4                   | 0.09                       |

| 0.5                   | 0.12                       |

| 0.6                   | 0.14                       |

| 0.7                   | 0.16                       |

| 0.8                   | 0.18                       |

| 0.9                   | 0.23                       |

| 1                     | 0.25                       |

The capacitance and the duration of compensating the sag was ploted as illustrated in figure 4.16.

Figure 4.16: Variation of Capacitance of supercapaciotor vs duration of sag compensating capability

It was found that as the capacitance increases, the duration of sag mitigating capability also increases.

# 4.2.1 Harmonics of injected voltage C.lk

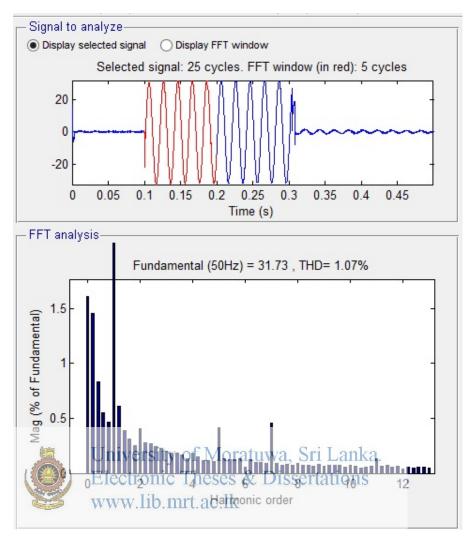

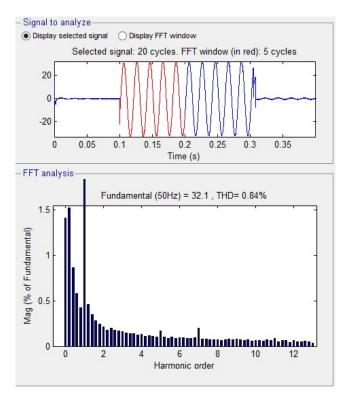

For a three phase sag of 50% for 0.2s duration, Total Harmonic Distortion(THD) levels of the injected voltage at the primary side of the injection transformer for 5 no of cycles was monitored for the battery energy option and the 1F super capacitor storage, both at an initial voltage of 160V. Results are shown in the figures 4.17 and 4.18 respectively.

Figure 4.17: THD of the injected voltage at the primary side of the injection transformer for battery storage

Figure 4.18: THD of the injected voltage at the primary side of the injection transformer for super capacitor storage

It was noticed a significant reduction in the THD levels for super capacitor energy storage.

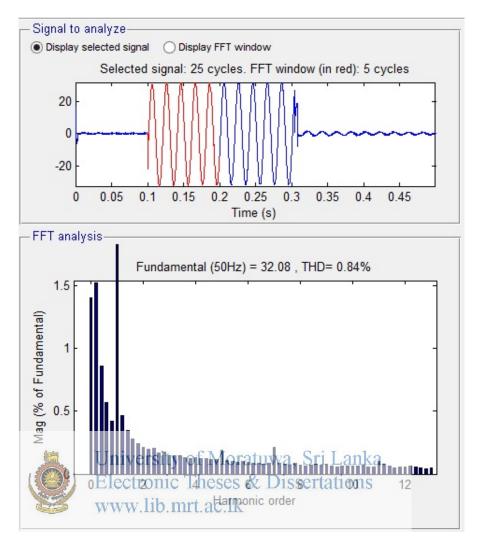

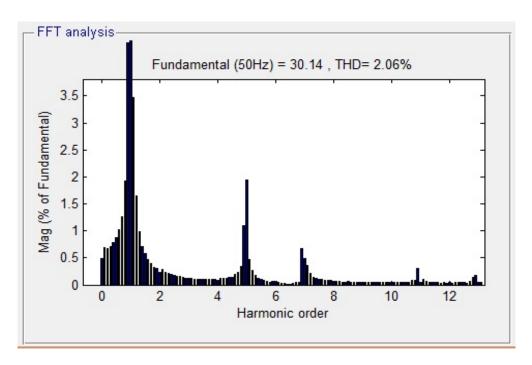

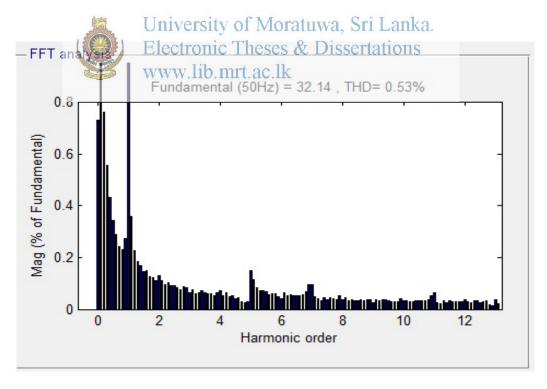

Capacitance of the Super capacitor was varied from 0.1 F to 1F and THD levels for 10 cycles of the injected voltage at the primary side of the injected transformer was monitored as illustrated in the figures 4.19 and 4.20.

Figure 4.19: THD of the injected voltage at the primary side of the injection transformer for 0.1F super capacitor

Figure 4.20: THD of the injected voltage at the primary side of the injection transformer for 1F super capacitor

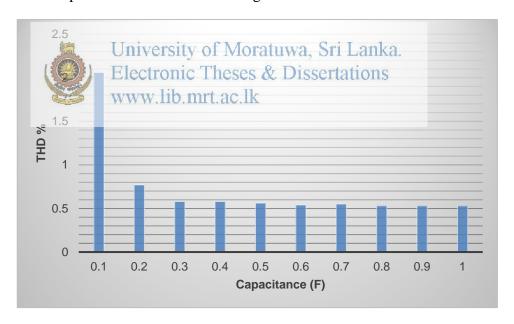

Variation of the THD levels against the capacitance of the super capacitor was tabulated in the table 4.6.

Table 4.6: Variation of THD for 10 cycles of the injected voltage at the primary side of the injection transformer for capacitance of the super capacitor

| Capacitance (F) | THD (%) |

|-----------------|---------|

| 0.1             | 2.06    |

| 0.2             | 0.77    |

| 0.3             | 0.58    |

| 0.4             | 0.58    |

| 0.5             | 0.56    |

| 0.6             | 0.54    |

| 0.7             | 0.55    |

| 0.8             | 0.53    |

| 0.9             | 0.53    |

| 1               | 0.53    |

Results were plotted as illustrated in the figure 4.21.

Figure 4.21: THD of the injected voltage at the primary side of the injection transformer vs. capacitance of the super capacitor

A significant decrease in the THD levels of injected voltage was monitored with the increase of the capacity of the super capacitor.

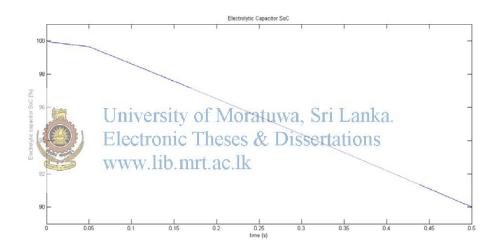

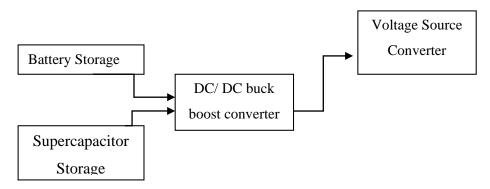

## 4.3 Integration of the conventional capacitor energy storage with the DVR

An ordinary electrolytic capacitor bank of 9F with initial voltage of 160V was connected as the DC storage of DVR and the response of the DVR was monitored. The simulation model is illustrated in the figure 4.22

Figure 4.22: DVR MATLAB model with Conventional capacitor storage

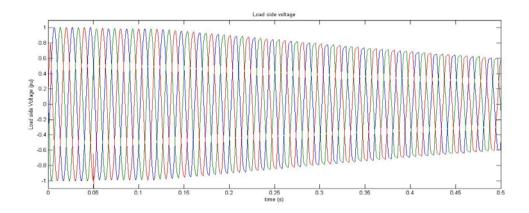

Super capacitor storage of same size and same initial voltage was integrated to DVR in order to compare the results between the ordinary electrolytic capacitor and the super capacitor. Accordingly the mean power delivered by the super capacitor and electrolytic capacitor was monitored as indicated in the figure 4.23 and 4.24 respectively. It was found that there is no significant discrepancy between various responses of the two different storage options.

Figure 4.23: SOC of super capacitor under 40% sag condition for 0.45s duration

Figure 4.24: SOC of electrolytic capacitor under 40% sag condition for 0.45s duration

It was observed that the SOC of both storages at the end of sag duration was almost same. But lot of fluctuations were observed in the super capacitor discharging characteristics than the electrolytic capacitor.